| Definition | Description | |

|---|---|---|

| (1) | SK hynix Logo | SK hynix |

| (2) | Module Capacity | Number of DDR4 DRAM storage in module |

| (3) | Module Configuration | Number of ranks of memory installed and Device organization |

| (4) | Memory Technology | DDR4 Product |

| (5) | Module Speed Grade | 1600K : 1600 11-11-11 1866M : 1866 13-13-13 2133P : 2133 15-15-15 2400T : 2400 17-17-17 2666U : 2666 19-19-19 |

| (6) | Module Type | U : 288pin Unbuffered DIMM R : 288pin Registered DIMM S : 260 pin Unbuffered SO-DIMM L : 288pin LRDIMM N : 288pin NVDIMM |

| (7) | Gerber Revision | JEDEC Reference design file used for this design |

| (8) | SPD Revision | JEDEC SPD Revision Encoding and Additions level |

| (9) | 2D Barcode | |

| (10) | Eco Logo | |

| (11) | CE Mark | |

| (12) | Country | Country of origin |

| (13) | Part Number | |

| (14) | Module Option Code | |

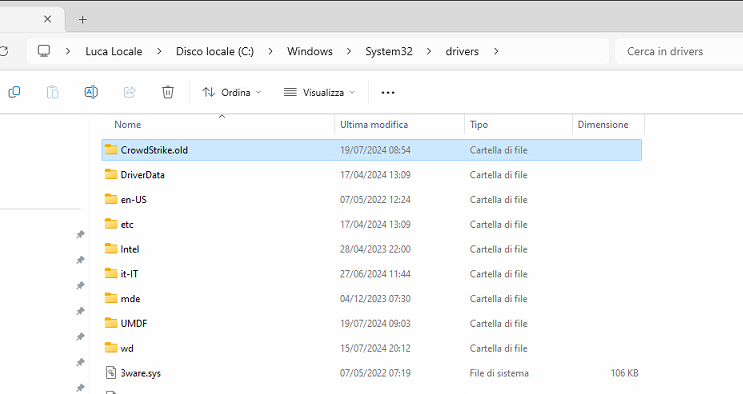

| (15) | Process Code | Internal use |

| (16) | Year & Week | Code of Manufactured Year & Week |

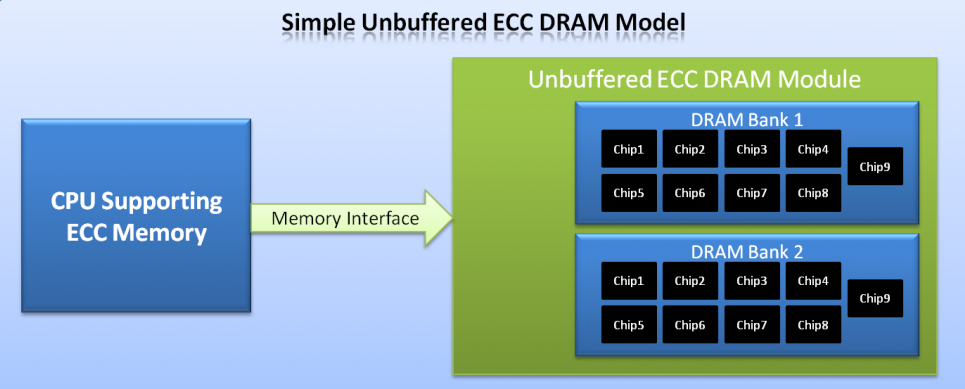

Unbuffered ECC

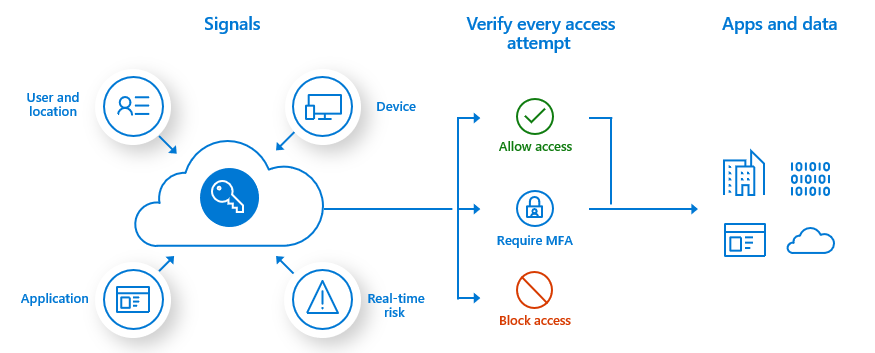

La differenza fondamentale è che i comandi di memoria di tipo Unbuffered vanno direttamente dal controllore al modulo di memoria, mentre nelle configurazioni di tipo Registered i comandi vengono inviati ai registri dei banchi di memoria prima di essere inviati ai moduli. Questo concetto può sembrare difficile, ma ecco la visione molto semplice / concettuale di ciò che sta accadendo. Nell’esempio sottostante il controller di memoria accede direttamente ai chip di memoria. Quanto sopra presume che il controller di memoria risieda all’interno della CPU come nelle moderne architetture. Guardando i sistemi più vecchi, il controller di memoria risiedeva nel Northbridge della CPU.

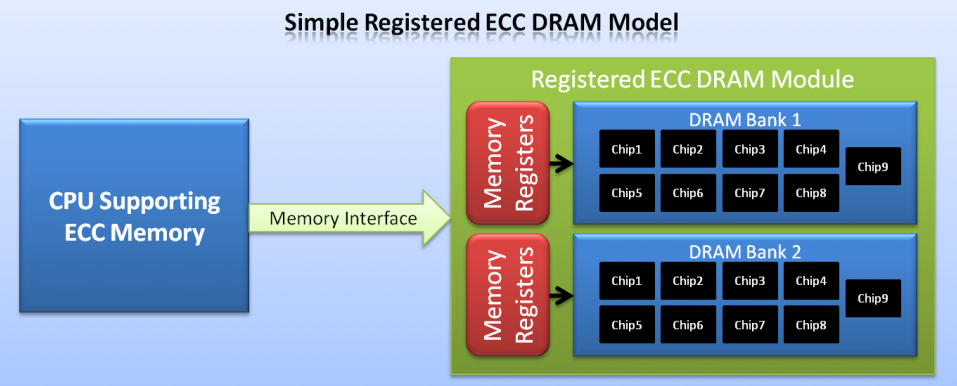

Registered ECC RAM

Qui la CPU comunica con i registri per i banchi di memoria di ciascun modulo. Da lì, questi registri comunicano con la DRAM. Le implicazioni sono duplici. Innanzitutto, dal lato negativo, le istruzioni richiedono circa un ciclo della CPU in più a causa dell’intermediario del registro. Sul lato positivo, questo buffering riduce il carico sul controller di memoria della CPU perché punta al registro intermedio dedicato rispetto all’accesso diretto alla DRAM. È più facile per il controller di memoria gestire un numero inferiore di obiettivi.

Per gli ambienti di virtualizzazione in cui le dimensioni e la larghezza di banda della memoria sono fondamentali per ottenere metriche di consolidamento e densità elevate, la memoria ECC Registered è generalmente la strada da percorrere.

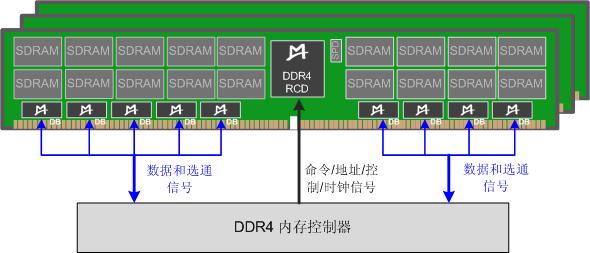

Le tipologie di memoria Registered hanno solitamente un chip dedicato nel centro del banco, nominato “Registered Clock Driver” come nella foto seguente.

Ok, ma che differenza c’è tra un process code es: AB e un process code AF ?